Cadence incorporates an AI 'super agent' to support developers while constructing EDA tools — the firm targets ‘over a trillion transistors’ by 2030, with AI aiding in the debugging and validation of intricate designs.

ChipStack AI Super Agent targets workflow friction amid growing packaging complexity and engineering shortages.

Receive 3DTested's top stories and detailed evaluations, delivered directly to your email.

You are now subscribed

Your newsletter sign-up was successful

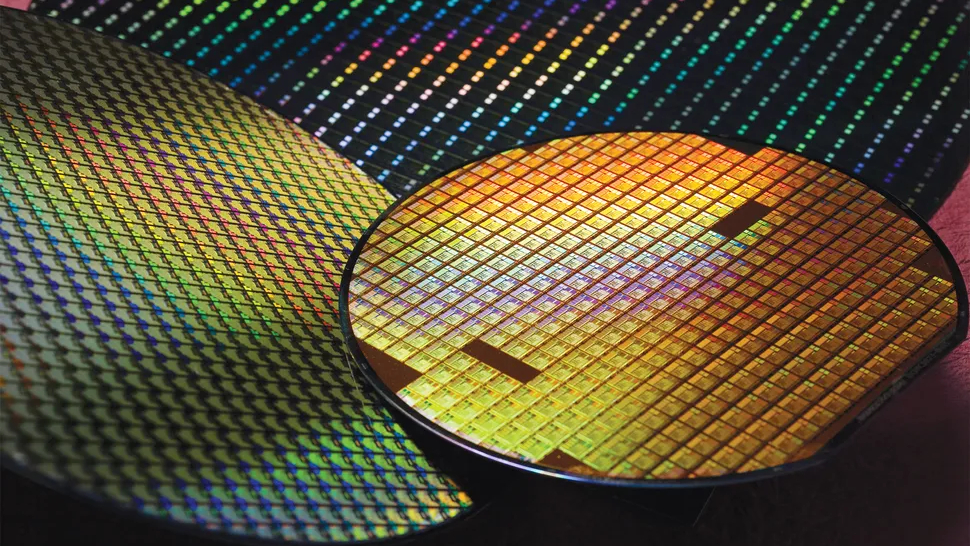

“A trillion transistors” appears to be an exaggeration, until it is no longer so. Engineering current cutting-edge transistors is similar to extending a framework that continues to expand indefinitely. Chiplets are attached as packaging piles components vertically, and parts such as power supply and connections are redirected whenever the physical dimensions change. Ultimately, the task of drafting the physical plan is replaced by managing all the components that link to it.

Such synchronization is the specific goal Cadence is pursuing via its recently introduced ChipStack AI Super Agent. Unveiled February 10, the framework integrates an AI-powered tool within Cadence’s electronic and design automation lineup, with the objective of aiding engineers to create, fix, test, and authorize complex Semiconductor initiatives more productively.

“We’re easily going to get over a trillion transistors… in the package, by the end of the decade,” Cadence Senior Vice President Paul Cunningham said in remarks to Bloomberg. “It’s a phenomenal increase in complexity.”

Emphasis on packaging

Cunningham’s focus on “in the package” is noteworthy because reaching a trillion transistors is not merely about scaling down components at sophisticated nodes, but integrating several dies into cohesive systems via Chiplets, 2.3D interposers, along with 3D stacking. Furthermore, as structural aspirations rise, so too does the pressure on design coordination.

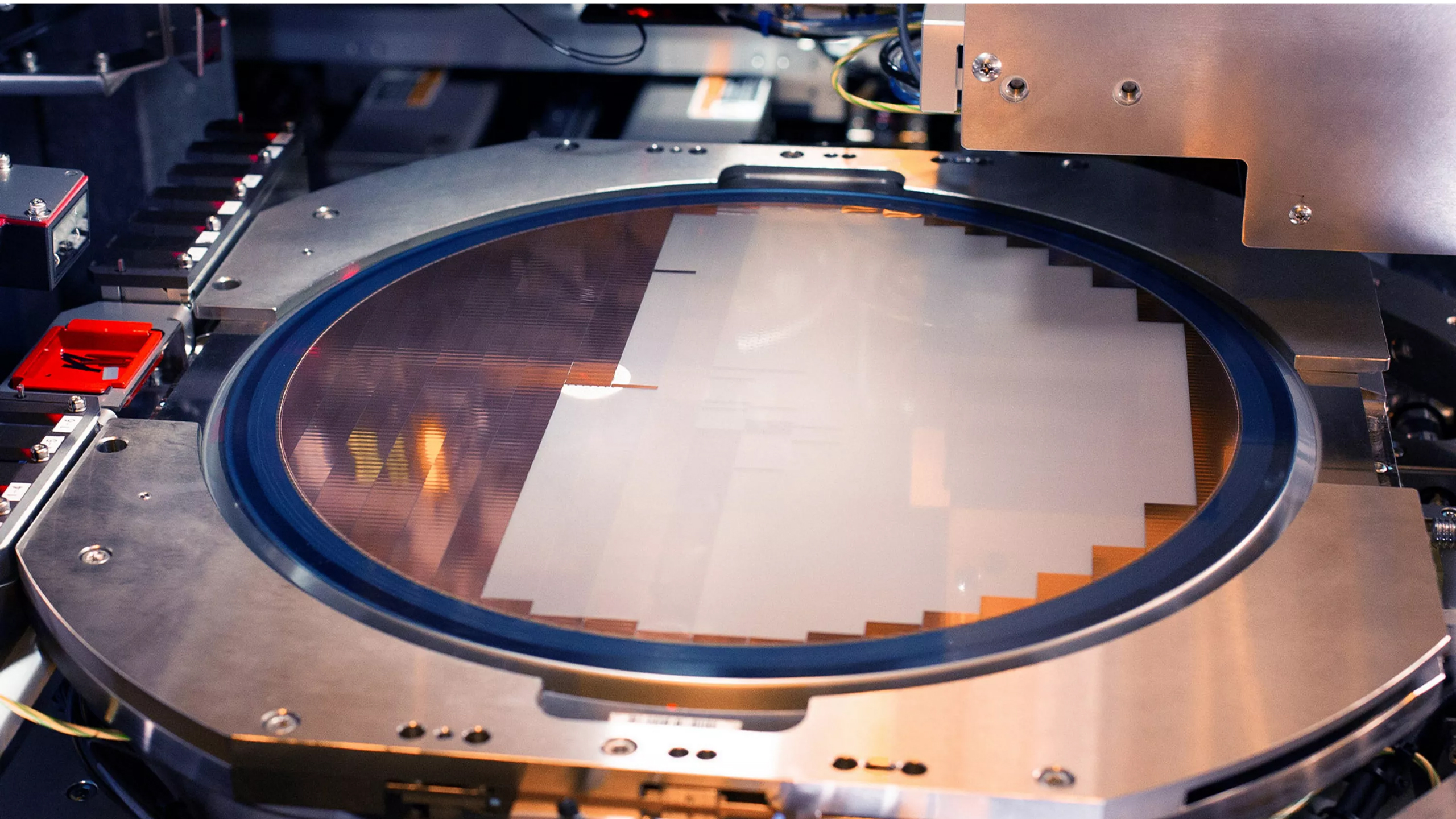

EDA has for a long time mechanized the design workflow, with synthesis, placement, routing, timing analysis, and verification all being highly algorithmic operations that operate on massive compute clusters. Multi-die packages bring about extra interconnect zones and power domains, complicate timing finalization over chip-to-chip links, and demand thermal analysis across layered silicon. Verification consequently no longer remains confined to block-level accuracy but reaches into system-wide communication among diverse elements.

Technical professionals supervise these exchanges via multi-tiered tool sequences, automation, requirements, and approval steps, though documentation can frequently reach thousands of lines, and debugging periods might last weeks. Cadence’s Super Agent operates atop that management level, serving as what the business defines as a specialized AI framework developed using a “mental model” of integrated circuit creation as opposed to a broad-use large language model. Engineers can communicate with the tool stack through natural dialogue, initiating operations without needing to sift through every script or extensive menus.

“You can chat with all of the Cadence products, and they’ll talk back to you,” he remarked. “You don’t have to be the absolute scripting specialist. You don’t have to understand every elaborate function and navigation step in our visual interfaces. You can simply state, ‘Look here. This is the objective I have in mind.’”

Labor constraints

The Semiconductor Industry Authority (SIA) forecasts that the U.S. May experience a deficit of tens of thousands of sector employees by the decade's close. A significant part of that deficit is anticipated to impact engineers and technicians with postgraduate degrees. Although scaling up production plants under the CHIPS Act — and the associated labor deficits — typically garners the most notice regarding the semiconductor skills gap, design mastery is just as scarce.

The engineering and creation of advanced-node chips necessitates experts in physical implementation, verification methodologies, packaging, signal integrity, and system architecture, along with various other abilities. Such positions necessitate extensive professional instruction and hands-on expertise, yet colleges and universities aren’t presently yielding degree holders at a pace adequate to meet anticipated needs and growth.

Thus, while it's perfectly fine to state “we’re going to break the trillion transistors mark,” the requirements for managing workflows grow in proportion as additional segments and links lead to expanded validation Circumstances and breakdown patterns. Unless work procedures undergo major adjustments, identical design methods will necessitate a growing amount of engineering time that will be tough, if not unfeasible, to meet.

Cadence asserts that the Super Agent is capable of providing efficiency boosts of as much as tenfold for specific assignments, a statistic that probably indicates focused advancements in routine, documentation-intensive workflows. Nevertheless, small decreases in cycle duration may significantly accumulate throughout extended project timelines and contribute substantially to speeding up production phases.

Agentic chip design

Generative AI has also introduced ambiguity across various software sectors, sparking debate about whether broad-purpose models might replace niche applications. EDA suppliers function within a highly restricted sector regulated by elements such as foundry process design kits and sign-off requirements. In this case, utilities such as timing analyzers and physical verification tools aren’t simply replaced by general-purpose models.

Yet, weaknesses are present: For several decades, employing EDA software has demanded proficiency in coding, workflow setup, and the distinct peculiarities of individual provider platforms. Such resistance has likewise contributed to keeping clients integrated. If a third-party AI helper were to overlay those applications and convert goals into software instructions, the interface boundary would start to weaken.

By incorporating a specialized model within its own architecture, Cadence makes certain that the dialogue system is a native component of the platform instead of being one of those overlays. This ‘Super Agent’ doesn’t supplant timing engines or verification tools; instead, it functions between the engineer and those utilities, deciphering intent and aligning it with certified workflows within the Cadence ecosystem. Because architectures are splitting into chiplets and stacked dies, restrictions will surely expand, and a system that understands a designer's request and converts it into accurately ordered tool functions might Minimize configuration errors and decrease troubleshooting durations.

Cadence isn’t the only firm in this situation. Synopsys and various competitors are recognized for being pursuing similar AI-assisted layers throughout their offerings, incorporating them into tool environments as a method to lower management burdens. Should Cadence effectively achieve this, it transforms the way groups manage the level of magnitude Cunningham is outlining.

Housing a trillion transistors in one package increases interfaces, validation, and the variety of potential failure modes. More dies result in additional cross-domain timing checks. Additional silicon stacks result in more thermal interactions to simulate. The coordination effort, as previously noted, increases in conjunction with that. If the supply of advanced engineers doesn’t scale at a matching rate, that synchronization strain must be handled in other areas. Either creation phases lengthen, or the actual productivity per developer rises. Cadence is working to ensure the second scenario occurs from within the toolchain.