First credible leak of an AMD Zen 6 processor pops up on Geekbench — ten-core CPU seems to have 32MB of L3 cache

The result itself isn't that meaningful, but it's notable in its very existence.

Get 3DTested's best news and in-depth reviews, straight to your inbox.

You are now subscribed

Your newsletter sign-up was successful

CPU leaks are a dime a dozen, and if we reported on every one, we'd report on nothing else. This latest one from the ever-watchful BenchLeaks bot is pretty notable, though, because it appears to be an early leak for an AMD Zen 6-based "Medusa Point" processor. That'll be part of the next-generation mobile family; seemingly, it's a 28W ten-core CPU meant for laptops.

[GB6 CPU] Unknown CPUCPU: AMD Eng Sample: 100-000001713-31_N (10C 20T)Min/Max/Avg: 1369/2006/1437 MHzCPUID: B80F00 (AuthenticAMD)Single: 1210Multi: 7323https://t.co/lxdcXm5aoE March 16, 2026

How do we know? Well, for starters, it's a ten-core processor, which simply isn't a configuration that exists outside of the Strix Point family, and this isn't that. Moreover, it's listed as running in an "AMD Plum-MDS1" system. "Plum" has previously been linked to the FP10 socket for next-generation AMD mobile parts, while "MDS1" is fairly evocative of "Medusa". Leakers have previously indicated that "MDS1" and "MDS2" would refer to the big and little Medusa Point processors, similar to Strix Point and Krackan Point.

Another key detail is the cache configuration. This ten-core CPU seems to have 32MB of L3 cache, which is simply not available on any of AMD's standard mobile processors. Chips that use the standard Zen CCDs, including the Ryzen AI Max and "Fire Range" desktop-on-laptop CPUs, have 32MB of L3 cache per CCD, but there's no way to have ten cores with one CCD as it stands. That alone pretty much marks this as a Zen 6 processor.

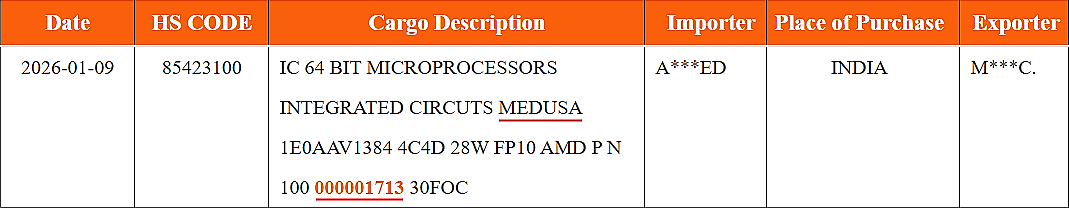

Article continues belowThe CPU is identified as "AMD Eng Sample: 100-000001713-31_N". That long string of numbers is called an "OPN", or Ordering Part Number. You won't find that OPN in any public AMD database just yet, although WCCFTech points out that the boys over at Planet 3DNow have it in their list (albeit with no details.) You will find it if you search that number on the NBD Data shipping logs, though.

As spotted by Videocardz, this listing at NBD directly connects the "1713" OPN to Medusa Point, the FP10 BGA package, and a 28W TDP. Though curiously, the NBD listing describes 1713 as "4C4D", which would seem to imply that the chips have four Zen 6 cores and four Zen 6C dense cores. It's possible that AMD is taking a page from Intel's book with its next-generation parts and including a pair of low-power CPU cores in the processor I/O die; we have seen it leaked that Medusa Point will be a chiplet design, unlike Strix and Gorgon.

As far as the actual benchmark result goes, there's not much to take away from it. This is obviously an early engineering sample, and the clock rates are very low. There's simply no way 3nm parts are limited to circa 2 GHz clock rates in their final form. In fact, looking at the actual result data, while it peaked at just over 2 GHz, the chip was in the 1.39 GHz range for most of the testing. We're tempted to be impressed at the score it achieved in that context, but the more honest and practical truth is simply that it's too early to say anything.

AMD has committed to launching the Zen 6 architecture this year, but most likely, we're only going to see EPYC 'Venice' processors in 2026. Consumer parts, including the Medusa Point mobile chips as well as Olympic Ridge desktop parts, will probably come later, likely to be announced at CES next year, with a release shortly after. We're expecting Olympic Ridge to go head-to-head against Intel's Nova Lake, which looks like it will be a beast CPU; we can't wait for the showdown early next year.

Get 3DTested's best news and in-depth reviews, straight to your inbox.

Follow 3DTested on Google News, or add us as a preferred source, to get our latest news, analysis, & reviews in your feeds.

-

usertests ReplyMoreover, it's listed as running in an "AMD Plum-MDS1" system. "Plum" has previously been linked to the FP10 socket for next-generation AMD mobile parts, while "MDS1" is fairly evocative of "Medusa". Leakers have previously indicated that "MDS1" and "MDS2" would refer to the big and little Medusa Point processors, similar to Strix Point and Krackan Point.

Though curiously, the NBD listing describes 1713 as "4C4D", which would seem to imply that the chips have four Zen 6 cores and four Zen 6C dense cores. It's possible that AMD is taking a page from Intel's book with its next-generation parts and including a pair of low-power CPU cores in the processor I/O die; we have seen it leaked that Medusa Point will be a chiplet design, unlike Strix and Gorgon.

K0B08iCFgkk:474

The leak aligns exactly with MLID's Medusa Point leak from months ago.

MDS1 = 4-core Zen 6 + 4-core Zen 6c + 2-core Zen 6 LP (+ an optional 12-core Zen 6 desktop chiplet)

So there's your 10 cores found by Geekbench, but with a document ignoring the LP cores and calling it "4C4D".

The completely new detail is 32 MiB of L3 cache for this product, if it's correct. Presumably that's unified, and would be far superior to Strix Point's 16 MiB + 8 MiB, or Krackan's 16 MiB.

However, Medusa Point is described as a sort-of Krackan successor that takes a step back on graphics (only 8 CUs) and a step forward on CPU performance, by allowing an optional 12-core chiplet to be attached. A decent baseline that can also become a good choice for overspec'd gaming laptops. -

KraakBal Yeah something is off, expecting 40mb L3 with 10 cores, but that for desktop ccds. So above comment makes sense.Reply -

usertests Reply

Zen 6 desktop CCDs will have 12 cores and 48 MiB. A 10-core desktop CPU should continue to have 48 MiB, like how a 9600X has 32 MiB (Intel tends to disable L3 cache down the stack, AMD doesn't bother except for some ultra-low end SKUs).KraakBal said:Yeah something is off, expecting 40mb L3 with 10 cores, but that for desktop ccds. So above comment makes sense.

Medusa Point could have 4x Zen 6 + 4x Zen 6c using 32 MiB, along with optional 12x Zen 6 using 48 MiB.

Geekbench could be detecting L3 cache for an unreleased product wrong, but maybe that happens more often with multiple CCXs, idk. Also, I think it's possible that Zen 6 LP cores are on their own CCX and not using the big L3 cache, and either have their own dedicated L3 cache or none at all.